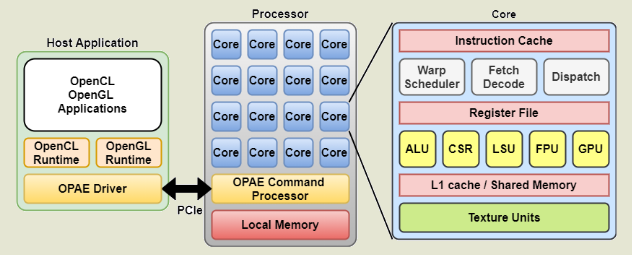

A group of researchers from the Georgia Institute of Technology is developing a research project Vortex , offering open gpgpu based on the RISC-V command set architecture aimed at performing parallel computing using the OpenCL API and SIMT execution model (Single Instructions, Multiple Threads), as well as research in research in Areas of 3D graphics and developing new GPU architectures. The project is still at the prototype stage using FPGA. Schemes, Descriptions of hardware blocks in the Verilog language, Simulator, Drivers and related project documentation distributed under a BSD license.

This form provides typical ISA RISC-V, extended by some Additional instructions , Required to support GPU functions and flow control. When developing, the authors of the project tried to minimize the changes in the RISC-V command set architecture, if possible using the already available vector instructions. A similar approach is also applied in the RV64X project, which also develops an open GPU based on RISC-V technologies.

Vortex features for graphics processing are still limited. declared about the implementation of OpenGL ES support based on Vortex, but in the GPU itself only implemented instructions “Tex” for Accelerating texture processing, which is performed at the fragment shader level. The built-in rasterizer is missing – all processing of geometric operations is performed on the side of the system CPU, and the basic primitives for points, lines and triangles, as well as processing fragments, depth and transparency, implemented using the OpenCl kernel.

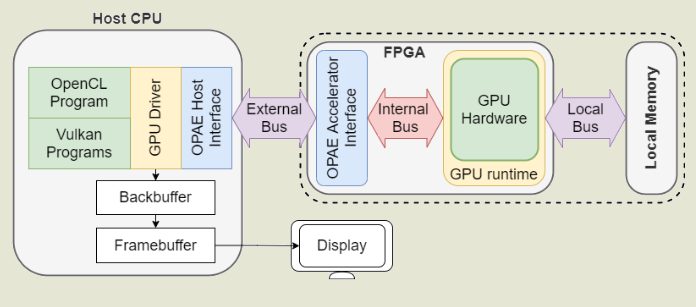

In the future, it is planned to implement the ISA extension-specific ISA graphics, add support for API CUDA and VULKAN, as well as expansion to accelerate machine learning and data analysis systems. For application development, it is proposed to tools , including adapted to work with Vortex options POCL (Compiler and Runtime OpenCL), LLVM / Clang, GCC and Binutils. The simulation of the chip operation is supported using Verilator (Verilog-Simulator) and SIMX (Software Simulation).

Main features of Vortex:

- Support for the RISC-V RV32IMF command set architecture.

- Scaling chip to 64 cores with optional caches L2 and L3.